LFO をパネルにマウントしました。回路図も清書したので設計・製作をまとめました。

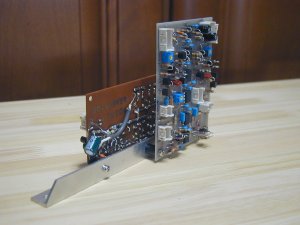

パネルへのマウント

パネルへの取り付けはこんな風にしました。ノイズジェネレータと同居です。

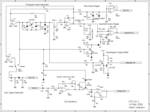

回路図

回路図はこちら。1系統分のみです。実際にはこれとほぼ同じものがもう1系統入っています。

sync 出力は、2系統目の三角波発生器のシュミットトリガー U1 のネガティブに入れます。

実装の反省点

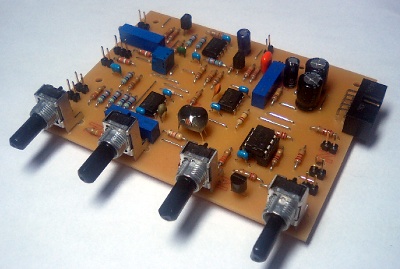

今回の製作はかなりてこずりました。何に苦労したかというと

– パタン設計時にべたアースを近接させすぎた

この写真はTL082の8ピンを裏から撮ったものです。素人泣かせの近づき具合を感じ取っていただけると幸いです。

特に後者が厳しく、1個ハンダ付けするたびにルーペとテスターで確認しながら実装するハンダ付け修行になってしまいました。

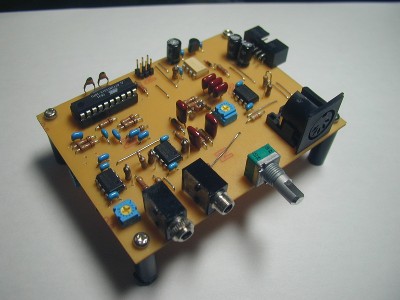

設計ミスについて

設計ミスは今後再発防止のため忘れないよう個別に記録しておきます。

– Q1 まわりは双方向の定電流回路だが、はじめこれは単純に 2.4k の抵抗だった。するとツェナーダイオードからの電圧が正負非対称に。(非対称な電源からの悪影響)

– 回路図には書かなかったが、発振スピードを落とすと、U2 積分回路が入力オフセットの悪影響を受け、三角波の登りと下りのスピードが著しく違ってしまった。これを解決するためU2には実際にはバイアス電圧がかかっている。

– R9 は当初の設計では220Ωだったが、最低スピードが速すぎてしまった。基板に部品を載せてから値を決めなおした。

– S/H のプリアンプのゲインが当初高すぎた。高すぎると、入力電圧が負に大きく振れたときQ2のゲートドレイン間電圧がピンチオフ電圧を下回ってしまい、スイッチオフ時にもかかわらずC5の電荷がQ2を通してもれてしまう問題があった。プリアンプのゲインを落とし、U3のポストアンプのゲインを高くした(1倍から3倍に変更)

– R1 が抜けていて当初 sync がうまくかからなかった

– R6 が V- ではなく GND に落とされていて、Q2のオフ電圧がとれず S/H が入力をホールドしなかった。

うわー、恥ずかしい。

設計失敗集は本家でアーカイブしてゆくかもしれません。

(別件でももう一つ見つけています)

お疲れさまでした♪

僕もパターンのミスはしょっちゅうです。パターン図を印刷して蛍光ペンで回路図とチェックはするのですが、それでも部品が反対だったりします。

部品さかさま私も VCF でやっちゃいました(トランジスタだったので助かった、というオチもつきました)。CADの手厚い助けのもとでも間違ってしまう私ちょっと情けないです。手でパタン設計していた頃はもう間違いのオンパレードで切り出しナイフが出ずっぱりでした(悲しいことに今でも使ってます)。