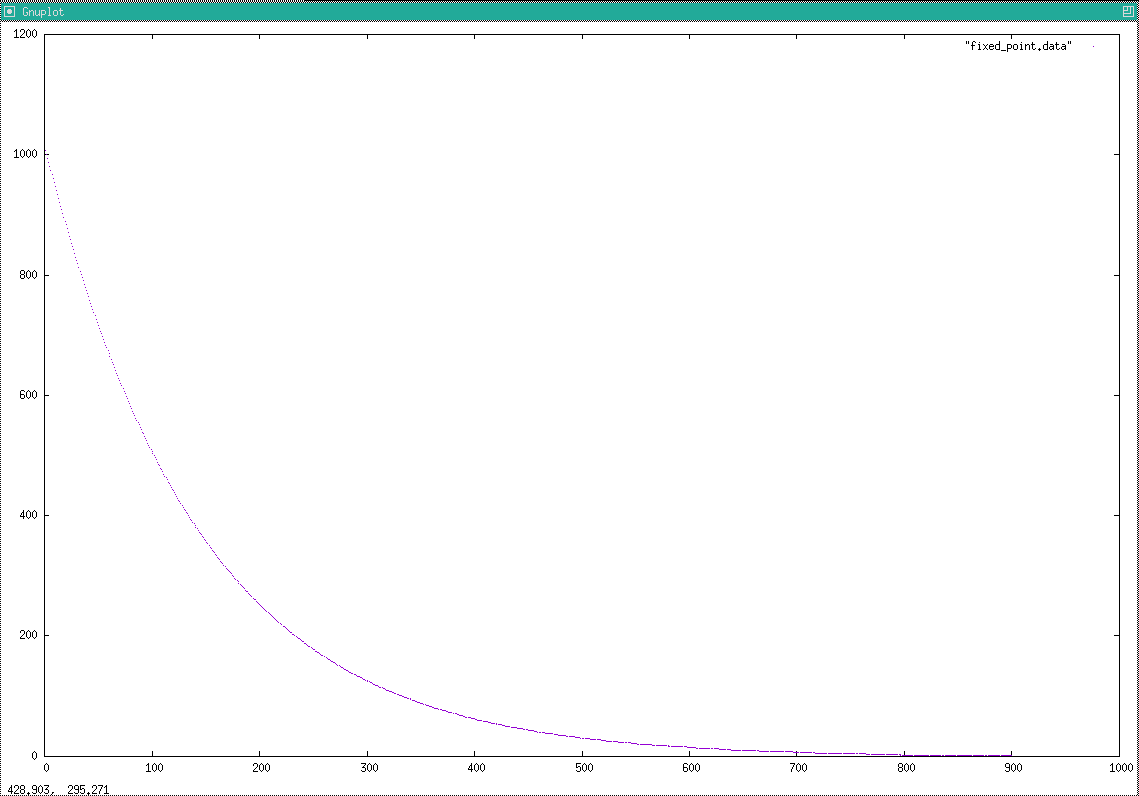

前回の記事で書きましたが、エンベロープジェネレータを試作基板に載せて設計が妥当かを検証していましたが、性能的にどうにも気に入りません。出力は PWM なのですが、48 MHz クロックで PWM を行うと解像度にはだいたい以下のような選択肢があります

- 20 kHz 更新周期、1024 ステップ (10bit)

- 10 kHz 更新周期、2048 ステップ (11bit)

- 5 kHz 更新周期、4096 ステップ (12bit)

つまり PWM 方式を使う限りタテ(振幅)の分解能とヨコ(時間)の分解能はトレードオフになります。色々実験した結果、タテの分解能は 11 bit ないと厳しくて、これより粗いと音量の階段状の変化が聞こえてしまいます。エンベロープジェネレータは、一般的には 10bit の実装が多いですが、ベロシティー対応すると広いダイナミックレンジが必要になり足りません。一方、2048 ステップでは 10 kHz の更新周期になりますが、この更新周期は可聴範囲であり、平滑用の4段 LPF のカットオフ周波数を 1 kHz とかなり低く設定しても「キーン」というノイズが聴こえてしまいます。一旦気づいたら簡単に聞こえるようになってしまうのでもう使えません。

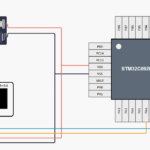

ということで、STM32C092 で満足のゆくエンベロープを出力するには外付け DAC が必要、しかし過去に検討した通り DAC を駆動する I2C 通信がコントローラを占有しすぎるので間に合いません。12 bit DAC 内蔵のもっと高級なマイクロコントローラを使えば解決しそうですけれども、でもエンベロープジェネレータ本体の実装は、コンデンサの充放電をシミュレーションしているだけです。コントローラを高くするのは何か納得がゆきません。がっつりスケジューラを書いて気合の入った実装をすれば DAC 外付けもできそうですけれども、充放電のシミュレーションするぐらいなら、アナログ回路でコンデンサの充放電を行うのもあり?とも思います。デジアナハイブリッドというのも Analog3 らしくて楽しそうです。とりあえず検討をしてみることにしました。アナログ回路を外付けしたらそっちの方がコントローラを良くするよりも高くつきそうなんですけれどもね。

Analog3 ではパラメータは数値制御が基本なので、コンデンサの充放電をアナログで行うなら電圧制御が必要です。アナログの電圧制御エンベロープジェネレータというと CEM3310 は現行品なら AS3310 などが代表的で、その動作原理は今一つ理解できていなくて興味があるのですが、データシートのブロックダイヤグラムを見る限りディスクリートで組むのは難しそうです。そちらはいつかじっくり研究することにして、今回は以前検討した OTA を利用した電圧制御抵抗を流用してみることにします。

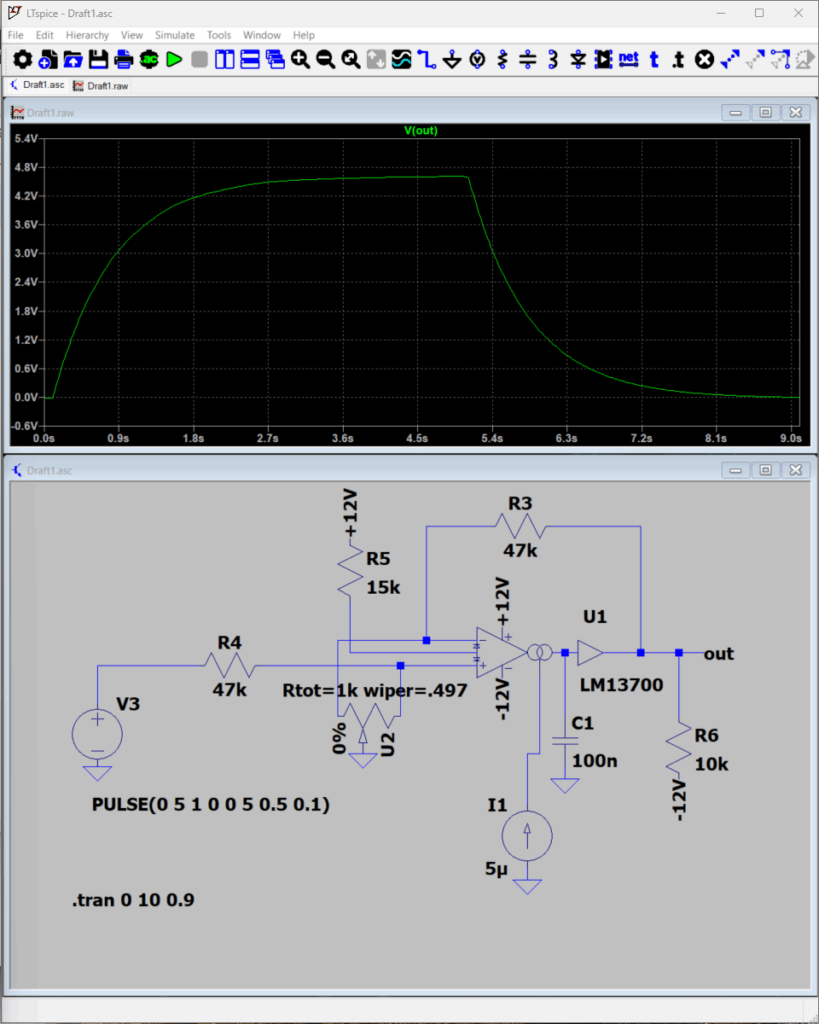

しかしよく見ると記事の中の電圧制御抵抗の回路が間違っていました。出力バッファは V- に抵抗を介して落とさないといけないのですがそれが抜けています。それでよく動いていたなあと思います。あと正しくは電圧制御でなく電流制御でした。回路を修正して電流制御の充放電回路が作れることを再確認しました。

OTA を使うと出力にオフセットが出ることを避けるのが難しいため要調整になってしまうのが残念ですが今のところ致し方ありません。前回の検討では回路を全てハードウェアで作ったため大変煩雑なわりに従来の ADSR と同じ動作しかしませんでしたが、今回は DAC 数台と比較器を使って動作はソフトウェア制御にすることを考えています。

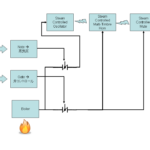

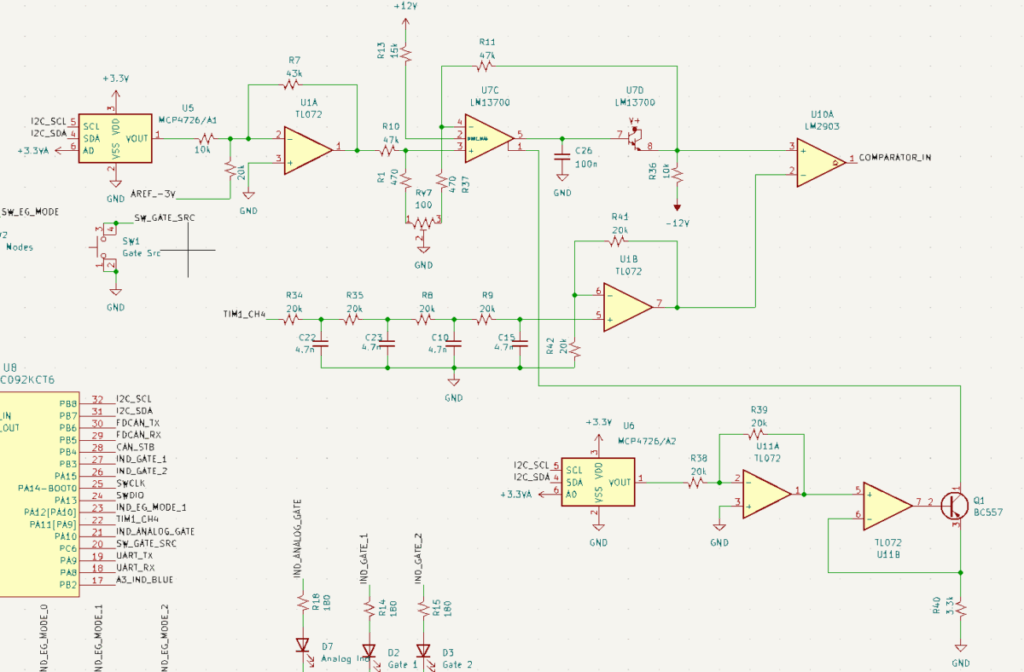

大急ぎで引いた回路図がこちら。電流制御抵抗を使った充放電回路の入力に DAC をつなぎ目標電圧を決めます。抵抗の制御にも DAC を使い電圧・電流変換回路をかましてあります。ここが洗練されていないのが少し気に入りません要再検討です。エンベロープジェネレータは状態推移を行う必要がありますがそれを手助けするために比較機が必要です。比較機の入力にも DAC をつなぐ必要がありますが、今手持ちの部品で I2C につなげる DAC は 2 個までなのでここは PWM を使います。

こうやって見てみると部品点数も多いしそんなに安くない DAC を三個も入れるので、懸念通り通り2ユニット組んだ暁には多分マイクロコントローラを良くした方が安上がりになると思います。開発もファームウェアを大幅書き換えになるので、こちらを試すとまたがっつり時間がかかってしまうでしょう。でも、これがちゃんと動くか興味がわきます。ということで少なくともブレッドボードでは組んでみて動くか確かめてみようと思います。コストという点では、DAC の代わりに PWM を使えばぐっと安くなります。この方式なら PWM の嫌なところも出にくくなるかもしれないという期待もあります。あとやっぱり、アナログ回路を介することによって「物理的に無理なこと」は起きないようにすると音にどんな影響が出るのか知りたいです。反面物理現象に反した曲線は描けないのが欠点ですけれども。

その他、回路図を描いてみたらあといくつか課題が見えてきました。回路の駆動は思うところあって ±6V としているので、これと比較器を利用してオフセットのソフトウェア調整を実装してトリマを外すことができるのではいの?とか、現在指数関数カーブしか出せませんがリニアも出すにはどうしようか、とか。