ほんに久々にシンセの話題です。

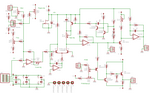

Analog2.0 シンセキットの試作はじわじわと進んでいます。

現在 VCO に着手しておりますが、若干問題につきあたりました。

さあ、どこが悪いでしょう?これだけでわかったあなた、かなりの達人です。私は気がつきませんでした。わかってりゃまずった設計のまま組み立てないですね。

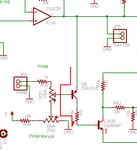

ヒントはこれです。

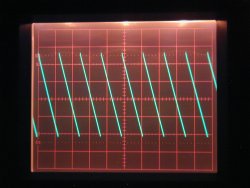

ノコギリ波出力

ノコギリ波出力

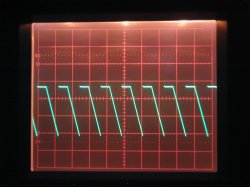

R32 と R33 を絞るとこうなってしまいます。

R32 と R33 を絞るとこうなってしまいます。

たてスケールは 2V/div です。なんかクリップしてますね。ちなみにクリップした状態だと IC1 がうんと熱くなります。

R32, 33 を絞ると、Q6 はベース接地回路なので、入力インピーダンスがむちゃ低くオペアンプの出力をみんな吸い込んじゃうんですね。IC1 や Q6 が壊れなくてよかったです。

回路をこんな風に修正したら問題が解決しました。

教訓:試作品でも製作前のブレッドボードは大事じゃ。忙しくてもせめてシミュレータぐらい使おう。