デジタル・アナログハイブリッドのエンベロープジェネレータを検討中です。その方が優れているという合理的な理由があるわけではなく、作れるのかな?そして作れるのならどんな音が出るだろう?という好奇心でやってます。出来上がってみたら完全に徒労でした、なんてこともあるかもしれません。

これまでは、OTA を使って回路を組んで、エンベロープジェネレータとしてはいちおう動くことを確認しました。それが以下の記事

しかし実際に動かしてみると、安定性と操作性に難があります。エンベロープジェネレータの肝である電圧制御抵抗を作るために VCA を使うわけですが、以前検討しましたが、ゲインは指数関数的に変化したほうが操作性が良いです。ところが OTA はリニア制御なのでソフトウェアを使って対応するか指数関数回路を加えるかが必要になり、どちらにしても違和感のなく操作できるようにするにはかなりの手間がかかります。それだけではなく、減衰が長くなると回路の安定性が悪くなり、今回組んだ実験回路では、減衰時間を伸ばしてゆくとある時点で突然全く減衰しなくなりました。これも OTA のリニア制御が災いしていると思います。OTA で VCA を組むとダイナミックレンジはあまり広くならないようです。つまり、エンベロープジェネレータを組むのに OTA はあまり向いていません。

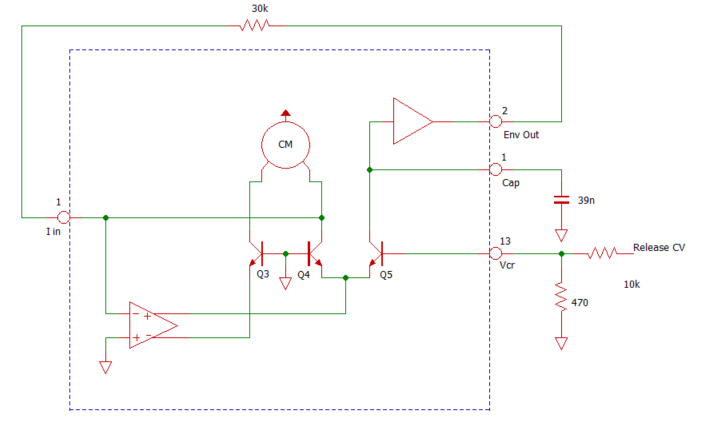

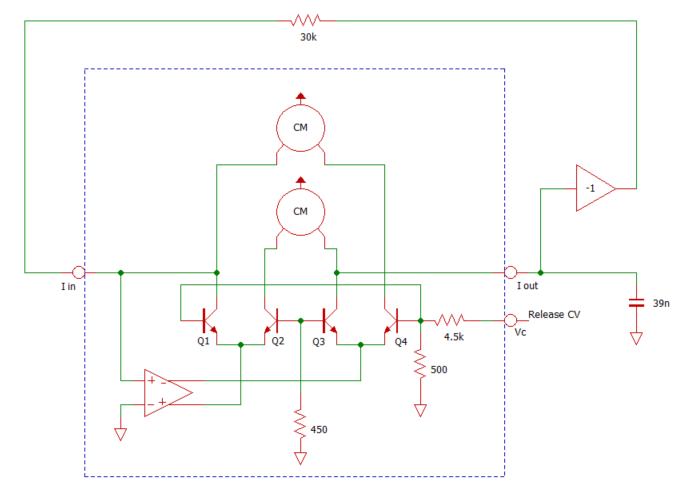

安定動作する電圧制御のエンベロープジェネレータなら、CEM3010、あるいは AS3010 という優秀な先輩がいます。先輩はどうしているのか見てみることにしました。AS3010 のデータシートに書かれているブロックダイアグラムを見ると、電圧可変抵抗は Blackmer Gain Cell とよく似ているように見えます。ブロックダイアグラム全体はかなり複雑なのですがその中から、一番単純そうなリリースに関わる部分を切り出してそれに推奨回路の部品を取り付けると以下のようになります

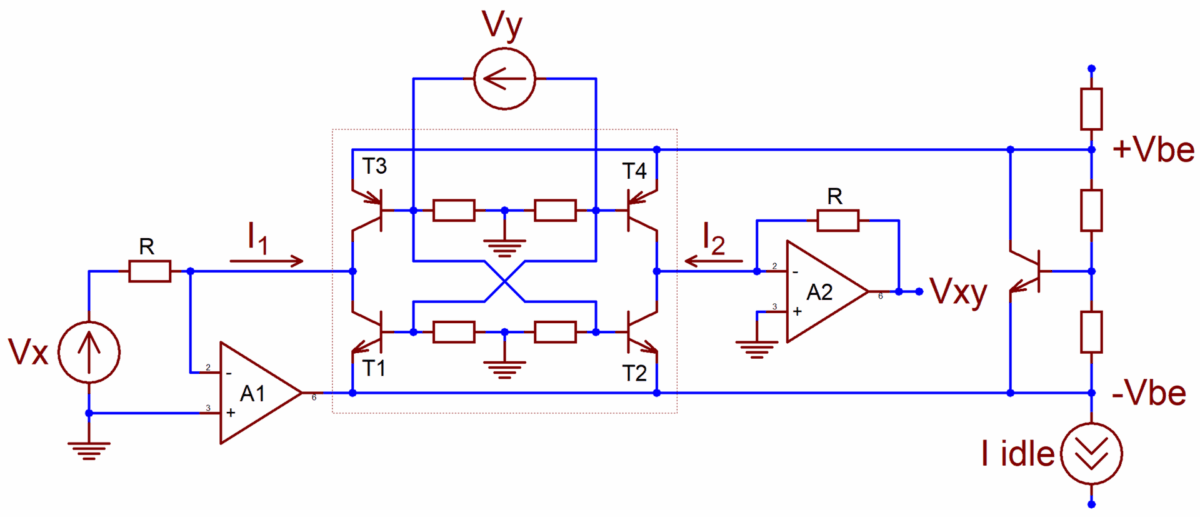

以下は一番単純な Blackmer Gain Cell の回路図です。3310 の回路はこれとはだいぶん違っていますが、増幅器の負帰還に Q4 を取り込み、Q4 と Q5 の不均衡から出力電流を指数関数制御しているところなど基本的な考えはよく似ているのではないかと思います。

素直に 3010 先輩を使うのも一つの考えですが、デジアナハイブリッドでやるならやはり ADSR の枠にとどまらずももっと変則的な曲線も作りたいです。というわけで、もう少し剥きだしの回路が欲しいです。とはいえ、リリース部分だけでも、Q3、Q4、Q5 のマッチングを取らなければならなそう、アタック・ディケイに関しては別回路で別のマッチングが必要、と、ディスクリートでは作れる気がしません。そもそも動作を増やすたびに回路を増やさなくてはならないようではハイブリッドで作る意味がありません。

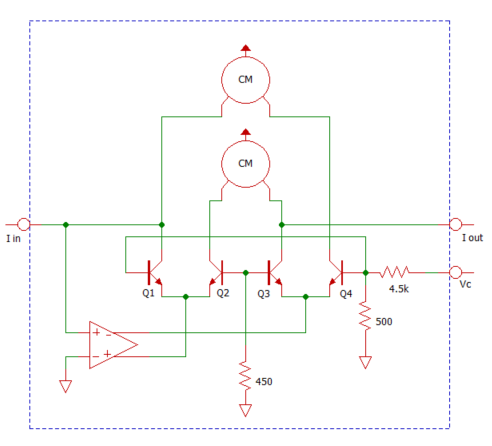

そこで同じく指数関数制御の VCA である SSM2164 に注目しています。まだ中身の詳細について勉強中ですが、はじめ Blackmer Gain Cell を使っているのだと思っていましたがどうもそうではないらしいことがわかってきました。Frey Operational Voltage Controlled Element と呼ばれているらしいです。でも、動作は似ているし基本的な考え方にも共通点が多いのではないでしょうか。そして、ブロックダイアグラムを眺めていると、CEM3310 は SSM2164 の回路とかなり似ているのでは?と感じるようになりました。解釈間違いが合ったら怖いですが、データシートに書いてあるブロック図を CEM3310 のブロック図風に書き換えてみると大まかにこんな構成になっているのではないかと思います。やっぱり入力電流の帰還にトランジスタを組み込みカレントミラーを使って対称の動作になっているトランジスタペアにベース電圧から不均衡を作り出して指数関数的にゲインを調整するところなどかなり似ている気がします。CEM3310 は SSM2164 回路の簡易版のようなものなのではないでしょうか。

そうすると、CEM3310 同様、以下のような外付け回路をつければエンベロープジェネレータになるのではないか、という目論見です。3310 では入力と出力が逆相だったので正のバッファが入っていましたが、SSM2164 では入力と出力は同相なので反転のバッファが必要なだけで、あとは同じ構成です。

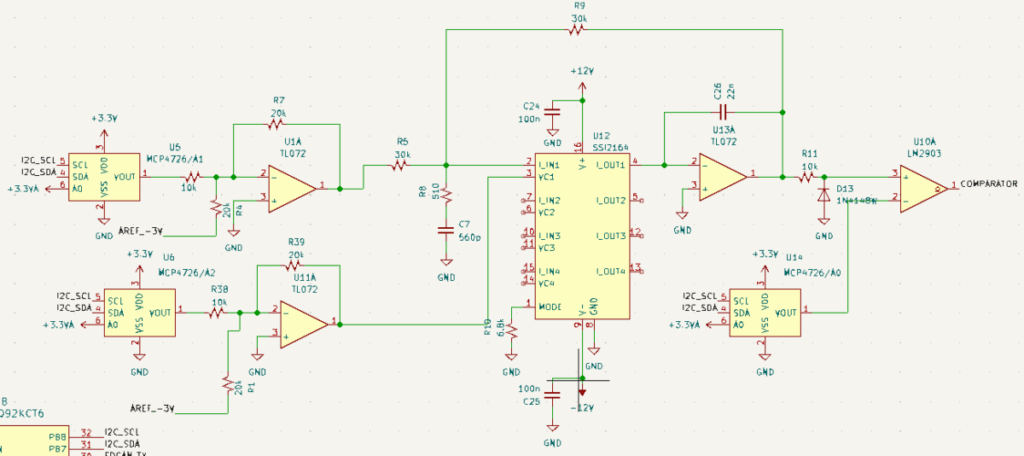

SSM2164 のダイナミックレンジは非常に大きいし、これは OTA の代わりに行けそうな気がします。というわけで、秋月電子から SSM2164 のセカンドソースの SS2164 を仕入れてきて、以下のような実験回路を組んでみました。

12bit DAC を三台も使うコスト度外視設計です。まずは PoC に集中してコストのことは後で考えます。基本的な動作原理は OTA 版と同じです。積分器に VCA を介して負帰還をかけることによって一次の LPF を組んでいます。状態遷移のきっかけをつかむために U10A の比較器を使っており、U14 の DAC から比較器に与える電圧によってベロシティーに対応できます。U5 の DAC を使ってエンベロープの元になる励起電圧を発生します。U6 の DAC を使ってエンベロープの動きの速さを制御します。U5 と U6 はいわばアクセルとブレーキ、ここをソフトウェアで細かく制御したいという目論見ですが、まずは単純な ADSR をやってみてこの回路がそもそも動くのか確認します。

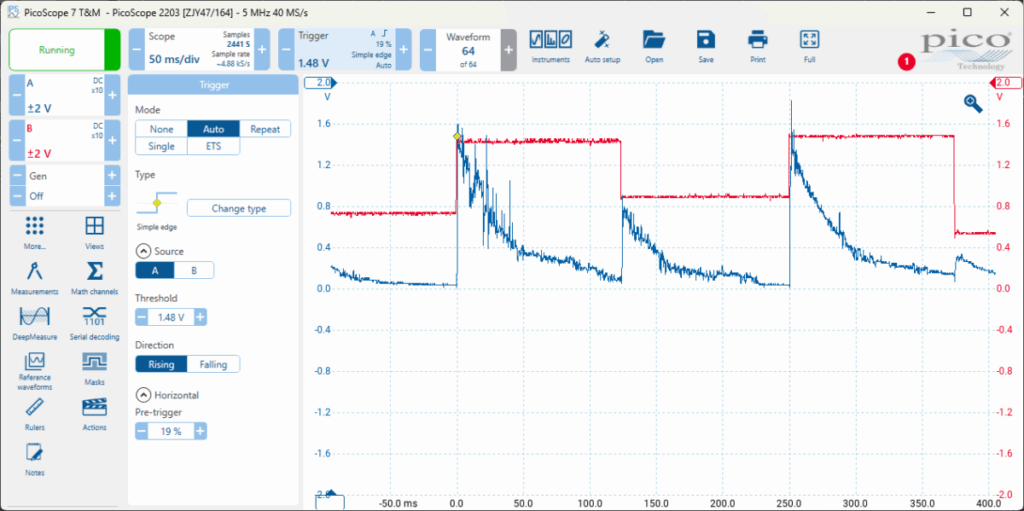

結果、ちゃんと動きました。曲線の安定性も OTA 使うより良いようです。

単純な ADSR ならファームウェアの実装は恐ろしく単純です。状態遷移の切り替わりに DAC 出力を変えるだけです。指数関数制御のおかげで、フィルタ時定数の制御もツマミの位置をそのまま電圧にするだけで良くなって非常に簡単になりました。

実際に指数関数の減衰曲線が得られているかをオシロスコープで確認しました。青線がエンベロープジェネレータの出力、赤線が比較器に入れているアタックレベルの電圧です。目論見通り指数関数の減衰ができています。またベロシティー制御も狙い通りにできています。

SSM2164 を使ったエンベロープジェネレータは、今のところ好感触です。ただ、一つ気になるのがリニア曲線の生成です。今の回路のままではできず対応するにはもう一工夫が必要そうです。