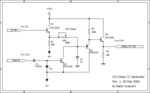

LFO ディレイの回路図やっと書きました。

鍵盤左手モジュレータから受け取った CV をバッファする機能とゲートトリガーを受け取ったら一時的に CV を落とす機能を持っています。LFO の深さコントロールは簡易的な VCA でやる予定です。

追記:うっかり参考にした回路図の出典を書くの忘れました。masa921さんの LFO Delayです。(ありがとうございます)

Q3 と Q4 はエミッタフォロワの2段重ねで、一見無駄ですが、VR1 が 500k とかなり大きいので、きちんとインピーダンス変換をすることが主目的です。NPN と PNP を組み合わせて Vbe 0.6V をキャンセルすることも狙っています。Q4 のエミッタが -6V でなくアースに落ちているのは間違いではなく CV がネガティブにならないようにと、0V 近辺に不感帯があるとモジュレータの悪精度があっても吸収してくれるためあえてそうしています。

VR1 が 0 に絞ってあると、+12V -> Q1 -> Q2 -> -6V という直結ラインが出来上がり、少しおっかないのですが、トリガー ON の一瞬のことだけならば大丈夫なようです(一度配線ミスで Q2 が常時 ON になっちゃいましたがそのときはあんまり大丈夫じゃなかった)(今気づきましたが Q1 のコレクタに 1k ぐらいの抵抗入れれば危なくなくなるかも。ディレイを絞りきっても立ち上がりがゆるくなる懸念は出ますが)

間違いや改善点等ありましたらご指導いただけるとうれしいです。