興味本位で SSI2162 という VCA チップを入手したんですが

https://www.soundsemiconductor.com/downloads/ssi2162datasheet.pdf

データシートに描かれている内部回路が全く理解できません。どういうことなの?と調べまくって大筋わかったのは、この IC の元ネタは SSM2164 という大変に普及した VCA で、基本動作原理は Blackmer Gain Cell という Blackmer さん (ブラクマさん?) という dbx のエンジニアだった人が発明したものだとか。なんか昔あったなーカセットテープのノイズリダクション、dbx とかドルビーとか、などと昔に思いをはせつつ。まずは Blackmer Gain Cell を理解しようと wikipedia の記事を読み始めてみました。別の VCA を設計中だったので完全に脱線です

https://en.wikipedia.org/wiki/Blackmer_gain_cell

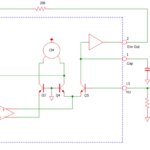

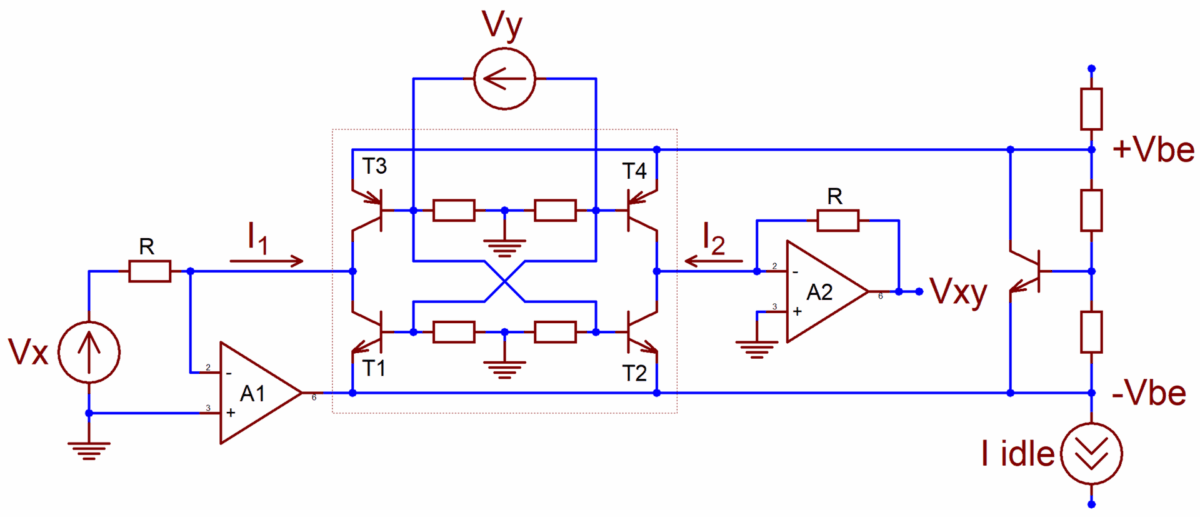

この回路についてはそもそも解説もなかなか見つからずやっと wikipedia に書かれているものを見つけたのですが、基本中の基本らしいゲインセルと呼ばれるこの回路を見てもやっぱりぱっと見ではわからない。

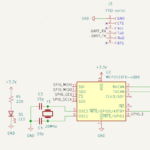

どうも T1・T2 の組みと T3・T4 の組みが上下二段のカレントミラーになっていて、そのおかげで入力側の I1 はどちらの向きでも I2 にミラーリングされるのが開始点らしいです。Vy に電圧がかかるとエミッタは共通ですから指数関数的に左右の電流に不均衡ができます。この状態で I1 に変化を加えると不均衡の比率に応じて I2 も変化すると、つまり可変増幅器になるようです。なので、制御電圧とゲインの関係は線形ではなく指数関数になります。これを感覚ではなく数式で理解したいですがそれにはまだ時間がかかりそうなので素早くシミュレータで動かして感触をつかんでみよう、ということで、やってみました

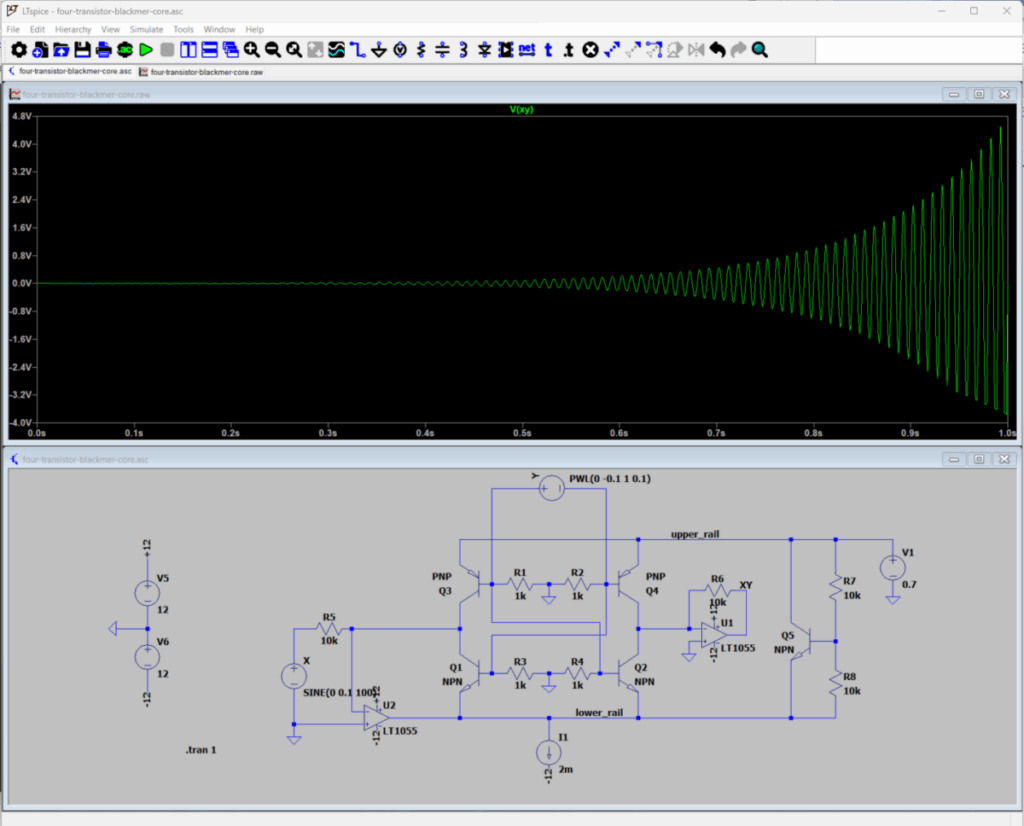

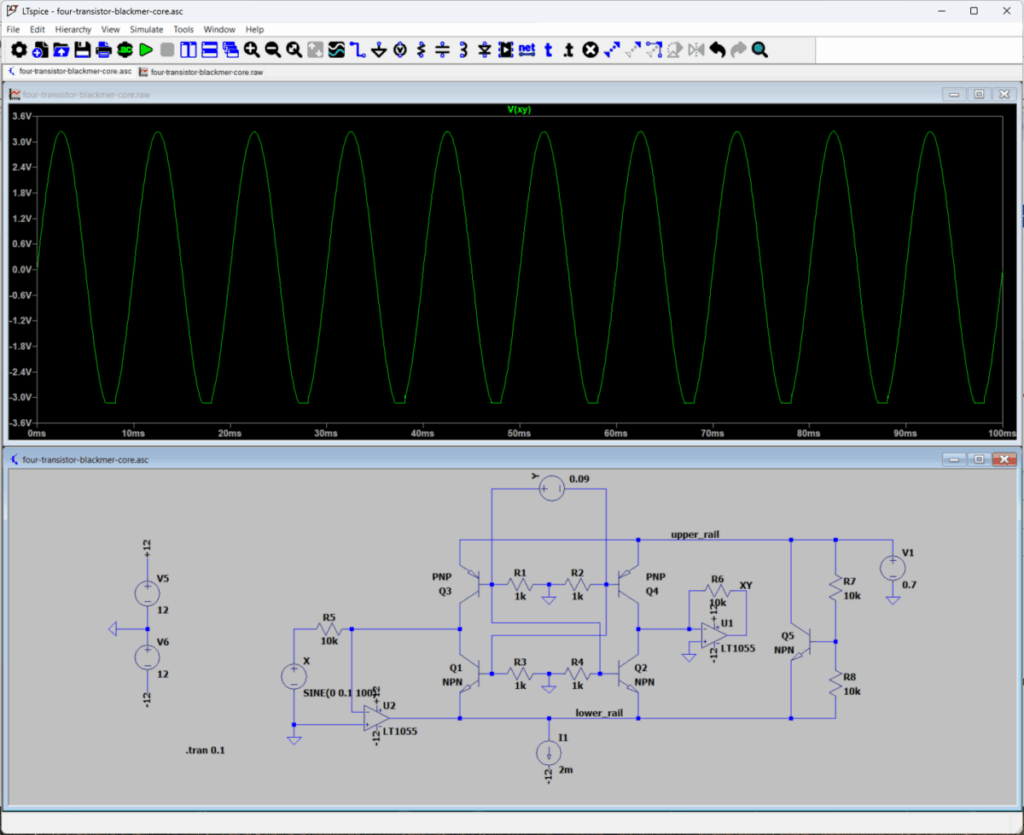

シミュレーションでは入力 (X) を振幅 0.1V の正弦波、制御電圧を -0.1V から 0.1V までリニアに振っています。ほんとに指数関数になってます。こんな回路をよくも思いついたものです。アナログ回路のこういう魔術的なところがアナログをやめられない(やめたくない)ゆえんの一つです。

ですがパラメータを極端に振りすぎて、CV の高いところでは出力は歪んでしまっています。

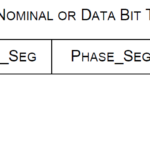

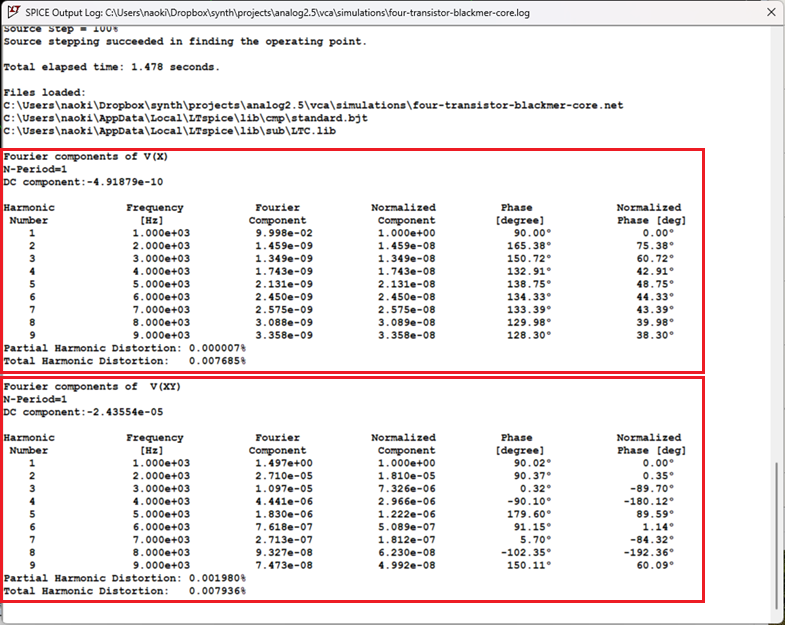

寄り道ついでに、LTSpice で歪み率を計算できないか調べてみました。どうやらできるようです。あれこれ調整が必要でしたけど細部は省いて、以下が使った実行コマンド(て呼ぶの?)です

.option maxstep=.0001

.option plotwinsize=0

.param freq 1k

.param cycles=2

.param delaycycles=4

.param simtime=(delaycycles+cycles) / freq

.param delaytime=delaycycles/freq

;.op

.tran 0 {simtime} {delaytime}

.four {freq} V(X) V(XY)以下のようにフーリエ解析の結果が出てきて、最後に歪み率が出てきますけれども、信号源である V(X) の THD がちょっと高すぎるのでは?これはシミュレーションの限界のようです。調整すると改善するかもしれませんが所詮シミュレーションなので細部を詰めてもあまり意味がないでしょう。

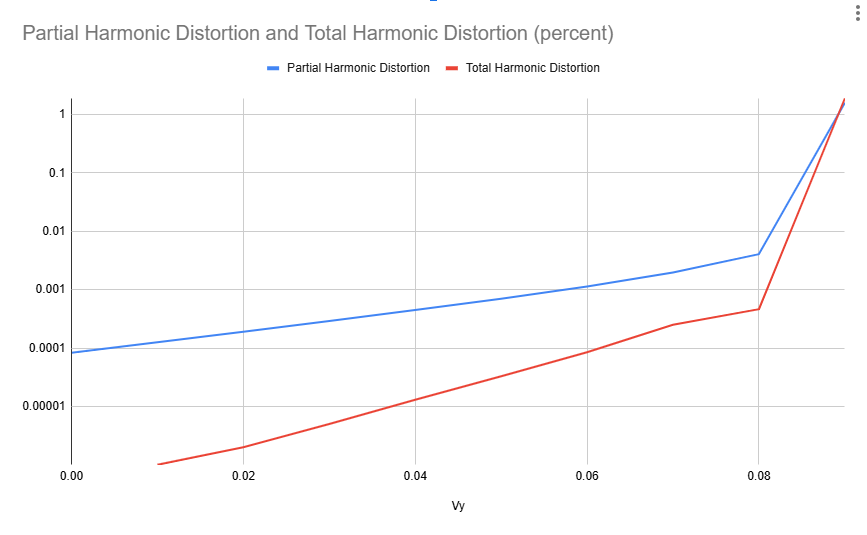

ちょっと乱暴ですが PHD と THD の値の出力と入力の差分をプロットしてみました。CV が上がるにつれじわじわと歪み率が増してある時点で崩壊するさまが見て取れます。

Blackmer Gain Cell は基本構造だけでは実用にはならないようでさらにさらに深みがあるようですが、この記事ではここまで。

あっせっかくだから検討に使った LTSpice ファイル置いておきます。ご自由にお遊びください

Version 4.1

SHEET 1 880 680

WIRE -96 -400 -208 -400

WIRE 80 -400 -16 -400

WIRE 160 -272 -288 -272

WIRE 304 -272 160 -272

WIRE 544 -272 304 -272

WIRE 656 -272 544 -272

WIRE 800 -272 656 -272

WIRE 800 -240 800 -272

WIRE -288 -208 -288 -272

WIRE 160 -208 160 -272

WIRE 656 -192 656 -272

WIRE -1072 -176 -1072 -224

WIRE -208 -160 -208 -400

WIRE -208 -160 -224 -160

WIRE -176 -160 -208 -160

WIRE -64 -160 -96 -160

WIRE -32 -160 -64 -160

WIRE 80 -160 80 -400

WIRE 80 -160 48 -160

WIRE 96 -160 80 -160

WIRE 320 -144 288 -144

WIRE 432 -144 400 -144

WIRE -64 -128 -64 -160

WIRE 800 -128 800 -160

WIRE -208 -64 -208 -160

WIRE 64 -64 -208 -64

WIRE 544 -64 544 -272

WIRE -1072 -48 -1072 -96

WIRE -1072 -48 -1152 -48

WIRE -656 -48 -736 -48

WIRE -560 -48 -576 -48

WIRE -288 -48 -288 -112

WIRE -288 -48 -560 -48

WIRE 160 -48 160 -112

WIRE 288 -48 288 -144

WIRE 288 -48 160 -48

WIRE 320 -48 288 -48

WIRE 80 -32 80 -160

WIRE 80 -32 -208 -32

WIRE 432 -32 432 -144

WIRE 432 -32 384 -32

WIRE -1072 -16 -1072 -48

WIRE 320 -16 288 -16

WIRE 656 -16 656 -112

WIRE 656 -16 608 -16

WIRE -288 16 -288 -48

WIRE 160 16 160 -48

WIRE 288 16 288 -16

WIRE -736 32 -736 -48

WIRE 656 48 656 -16

WIRE -208 64 -208 -32

WIRE -208 64 -224 64

WIRE -176 64 -208 64

WIRE -64 64 -96 64

WIRE -32 64 -64 64

WIRE 64 64 64 -64

WIRE 64 64 48 64

WIRE 96 64 64 64

WIRE -64 96 -64 64

WIRE -1072 112 -1072 64

WIRE -560 160 -560 -48

WIRE -528 160 -560 160

WIRE -288 176 -288 112

WIRE -288 176 -464 176

WIRE -64 176 -288 176

WIRE 64 176 -64 176

WIRE 160 176 160 112

WIRE 160 176 64 176

WIRE 544 176 544 32

WIRE 544 176 160 176

WIRE 656 176 656 128

WIRE 656 176 544 176

WIRE -736 192 -736 112

WIRE -528 192 -736 192

WIRE -736 224 -736 192

WIRE -64 224 -64 176

FLAG -1152 -48 0

FLAG -1072 -224 +12

FLAG -1072 112 -12

FLAG -64 -128 0

FLAG -64 96 0

FLAG -736 224 0

FLAG 288 16 0

FLAG -496 144 +12

FLAG -496 208 -12

FLAG 352 -64 +12

FLAG 352 0 -12

FLAG -64 304 -12

FLAG 432 -144 XY

FLAG 304 -272 upper_rail

FLAG 64 176 lower_rail

FLAG 800 -128 0

FLAG -736 -48 X

SYMBOL voltage -1072 -192 R0

WINDOW 123 0 0 Left 0

WINDOW 39 0 0 Left 0

SYMATTR InstName V5

SYMATTR Value 12

SYMBOL voltage -1072 -32 R0

WINDOW 123 0 0 Left 0

WINDOW 39 0 0 Left 0

SYMATTR InstName V6

SYMATTR Value 12

SYMBOL npn -224 16 M0

SYMATTR InstName Q1

SYMBOL npn 96 16 R0

SYMATTR InstName Q2

SYMBOL pnp -224 -112 R180

SYMATTR InstName Q3

SYMBOL pnp 96 -112 M180

SYMATTR InstName Q4

SYMBOL res -80 -176 R90

WINDOW 0 0 56 VBottom 2

WINDOW 3 32 56 VTop 2

SYMATTR InstName R1

SYMATTR Value 1k

SYMBOL res 64 -176 R90

WINDOW 0 0 56 VBottom 2

WINDOW 3 32 56 VTop 2

SYMATTR InstName R2

SYMATTR Value 1k

SYMBOL res -80 48 R90

WINDOW 0 0 56 VBottom 2

WINDOW 3 32 56 VTop 2

SYMATTR InstName R3

SYMATTR Value 1k

SYMBOL res 64 48 R90

WINDOW 0 0 56 VBottom 2

WINDOW 3 32 56 VTop 2

SYMATTR InstName R4

SYMATTR Value 1k

SYMBOL res -560 -64 R90

WINDOW 0 0 56 VBottom 2

WINDOW 3 32 56 VTop 2

SYMATTR InstName R5

SYMATTR Value 10k

SYMBOL voltage -736 16 R0

WINDOW 123 0 0 Left 0

WINDOW 39 0 0 Left 0

SYMATTR InstName X

SYMATTR Value SINE(0 0.1 1000)

SYMBOL res 416 -160 R90

WINDOW 0 0 56 VBottom 2

WINDOW 3 32 56 VTop 2

SYMATTR InstName R6

SYMATTR Value 10k

SYMBOL current -64 224 R0

WINDOW 123 0 0 Left 0

WINDOW 39 0 0 Left 0

SYMATTR InstName I1

SYMATTR Value 2m

SYMBOL voltage -112 -400 R270

WINDOW 3 26 100 VRight 2

WINDOW 123 0 0 Left 0

WINDOW 39 0 0 Left 0

SYMATTR Value 0.09

SYMATTR InstName Y

SYMBOL OpAmps\\LT1055 -496 112 R0

SYMATTR InstName U2

SYMBOL OpAmps\\LT1055 352 -96 R0

SYMATTR InstName U1

SYMBOL voltage 800 -256 R0

WINDOW 123 0 0 Left 0

WINDOW 39 0 0 Left 0

SYMATTR InstName V1

SYMATTR Value 0.7

SYMBOL npn 608 -64 M0

SYMATTR InstName Q5

SYMBOL res 640 -208 R0

SYMATTR InstName R7

SYMATTR Value 10k

SYMBOL res 640 32 R0

SYMATTR InstName R8

SYMATTR Value 10k

TEXT -1160 288 Left 2 !.option maxstep=.0001\n.option plotwinsize=0 \n \n.param freq 1k\n.param cycles=2\n.param delaycycles=4\n.param simtime=(delaycycles+cycles) / freq\n.param delaytime=delaycycles/freq\n \n;.op\n.tran 0 {simtime} {delaytime}\n.four {freq} V(X) V(XY)

参考資料:

Blackmer Gain Cell (Wikipedia)

https://en.wikipedia.org/wiki/Blackmer_gain_cell

A Brief History of VCAs (THAT Corporation)

https://thatcorp.com/a-brief-history-of-vcas/

SSM2164 Datasheet

https://www.alldatasheet.com/datasheet-pdf/view/49093/AD/SSM2164.html

SSI2162 Datasheet

https://www.soundsemiconductor.com/downloads/ssi2162datasheet.pdf

Patent: Voltage controlled elements (google)

https://patents.google.com/patent/US4471320A/en

ノートンアンプによる OVCE タイプの VCA (1) (シンセ・アンプラグド)

https://pcm1723.hateblo.jp/entry/20100716/1279288122