設計した MIDI/CV 回路の部分ごとに動作確認、回路を確定しました。最後に確定した回路はゲート出力、ゲートといっても少し特殊で、ベロシティー情報を出力電圧に乗せます。ベロシティーが最小なら出力は 0V なわけであり、それでもトリガをかけられるようにするため、ゲートオフ時には出力電圧は約 -2V に落ちます。そのため入力は二系統あり、一つはベロシティー信号を作る DAC から R45 に入っていく系統、もう一つはゲート ON/OFF を表す 0-5V 信号で P-JFET である Q10 のゲートに入ります。この FET は P 型ですからゲート ON 時、5V 入力時には Q10 がカットオフし、DAC 信号がそのまま出力に行きます。ゲート OFF 時には 0V 入力で Q10 は導通します。同時に DAC の出力も 0V に落とします。そうすると R43 を介して負電圧が入力されて出力は約 -2V になります。

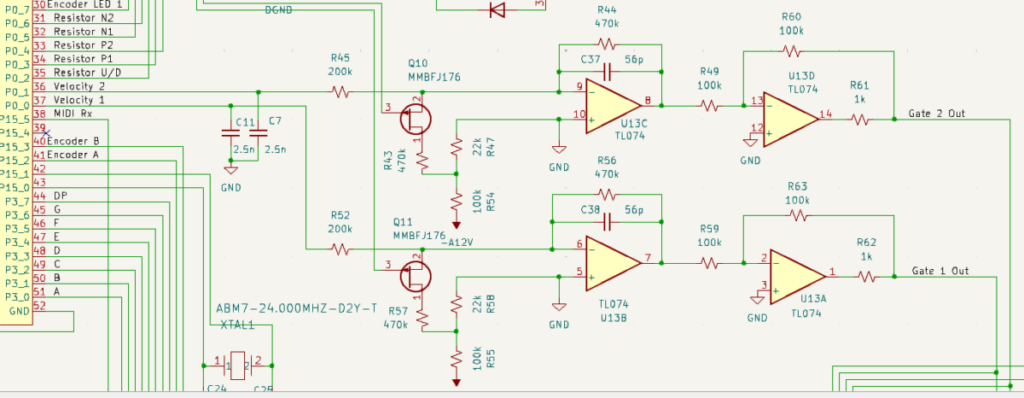

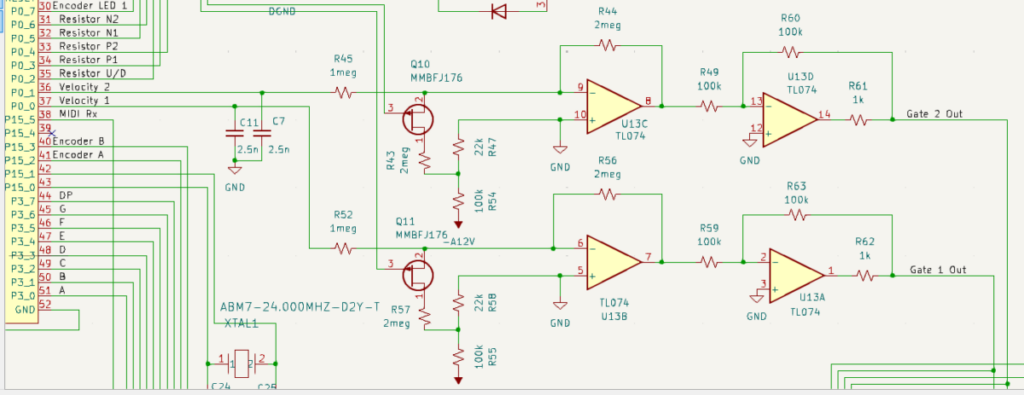

上の図が確定回路ですが、最初は以下のような回路でした。

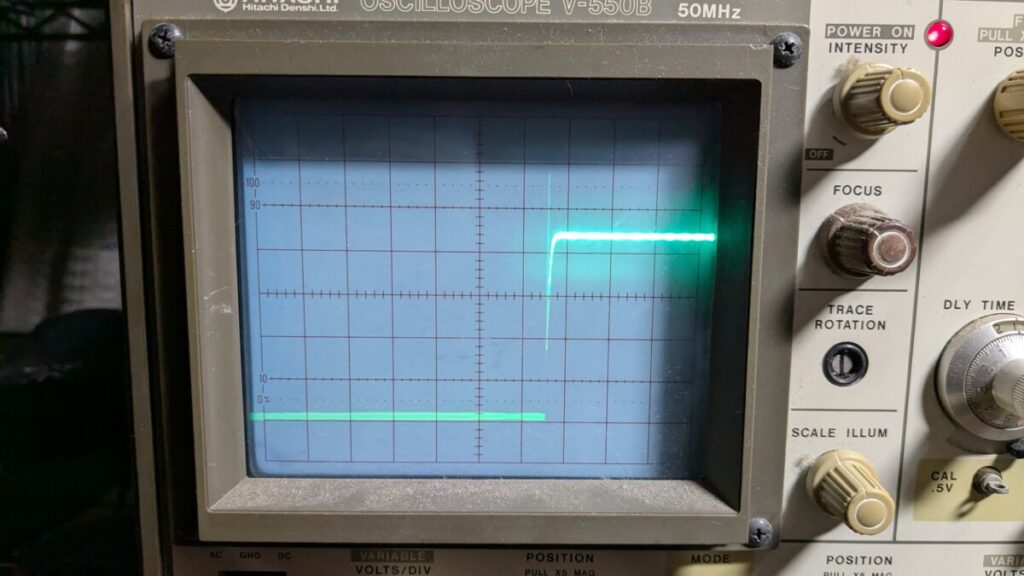

出力電圧は設計通りに出るのですが、実際に組んでみて出力を見てみると

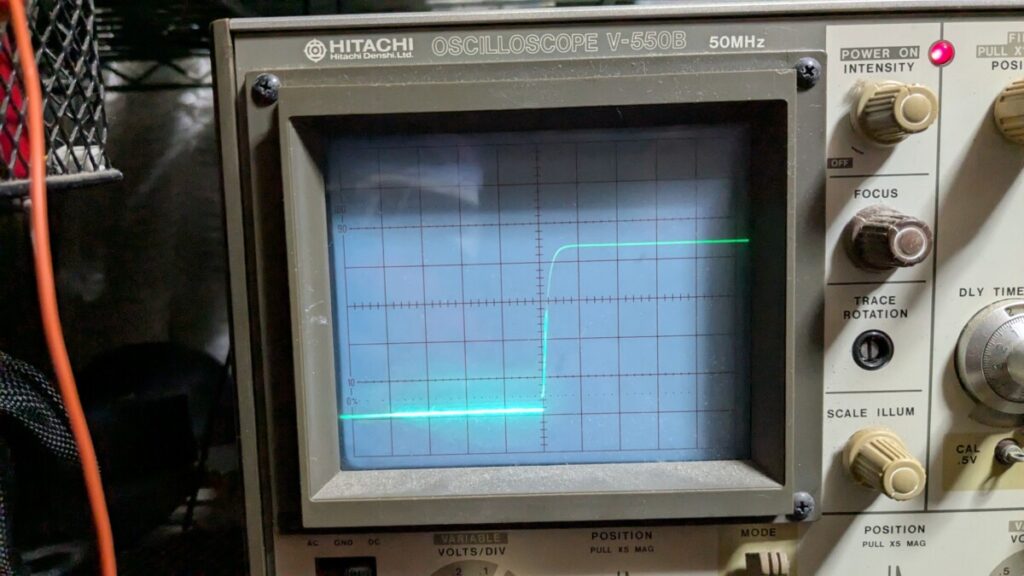

横軸は 1ms/div です。出力電圧は正しく、立ち上がりも十分に速いのですが、これ、オペアンプが発振しとります。実は、PSoC の DAC の出力インピーダンスは、この回路の設定だと 16kΩ と結構高く、その影響が出ないようにするために初段のアンプのインピーダンスを上げていることが問題になっているようです。あわてて 56pF のバイパスコンデンサを U13C U13B のフィードバックループに入れてみると

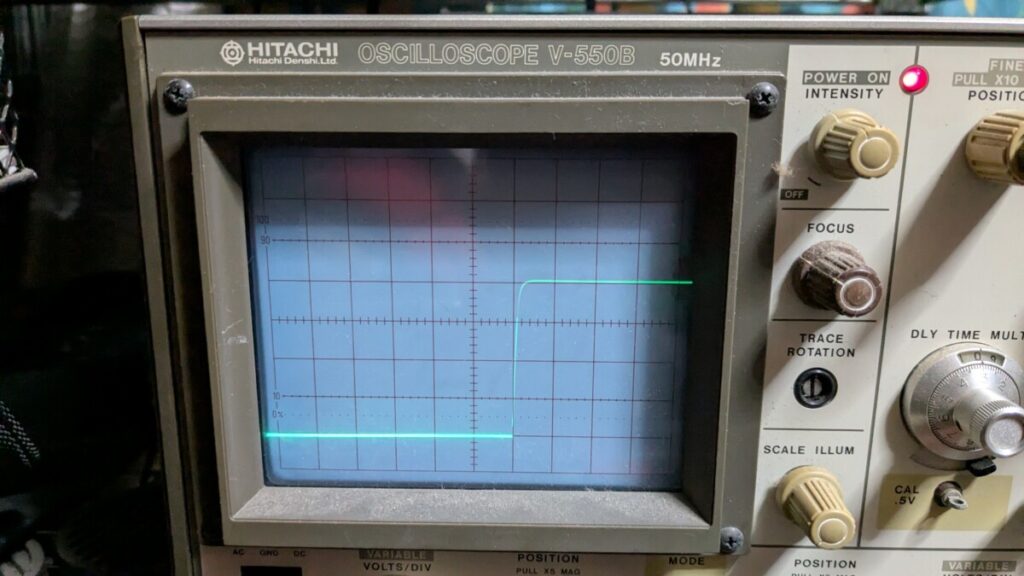

発振は止まりますが立ち上がりのエッジがちょっと鈍くなってこれは誤動作を誘わないか心配です。そこでコンデンサの容量を 3pF まで減らしてみましたが立ち上がり波形は改善されるものの発振の抑止としては弱くていけません。結局回路のインピーダンスが高すぎるのだ、と考えキャパシタは 56pF のままオペアンプまわりの抵抗値を下げてみたところ、良い感じに落ち着きました。

結果の回路定数が冒頭の回路図です。