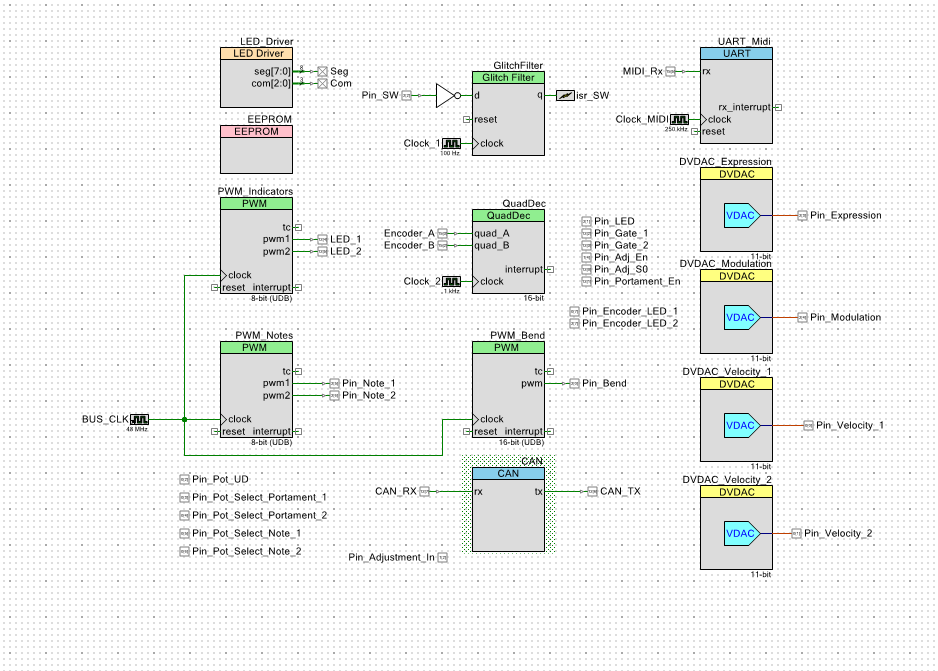

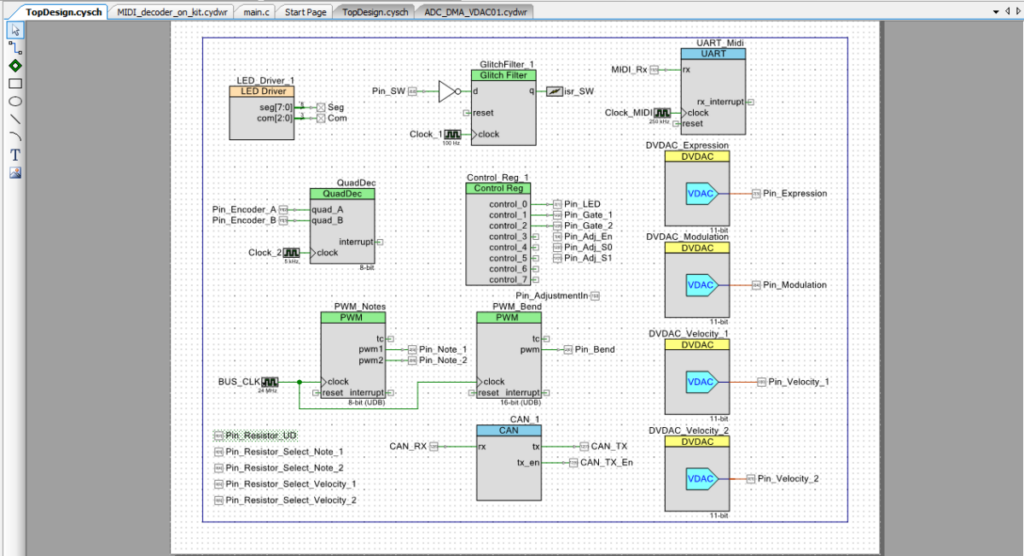

欲しい仕様が収められるプロセッサは PSoC が第一候補だったのですが、PSoC5 LP に収まりそうなので当初の予定通りこれに決定、チップ CY8C5888LTI とこれを搭載したキット CY8KIT-059 がほぼ同じ値段なのと、チップを基板にはんだ付けする自信がないためキットをそのままモジュールの基板に載せることにしました。GPIO ピンによっては特定用途のために部品がつけてあって邪魔ですがそれらのピンは避けて設計、ピンが足りなくなったら部品は外してしまう予定です。PSoC は安くないけど周辺ハードウェアをプログラミングできるため設計の柔軟性は抜群、外付け部品がとても少なく済みます。コンポーネントごとに制御用の API が用意されているので、自分で書くコードも少なくて済みます。つまり設計開発がとても楽です。

考えていた仕様をまずはできる限り PSoC 内のハードウェアで実装、ある程度固まってピン番号が決まってきたので、次には周辺回路を設計、時々 PSoC に戻ってハードウェア設計を変更、それに伴って周辺回路も修正、を繰り返しつつ予定していた仕様をひとつづつ追加、今多分 80-90% ぐらいまで来ました。

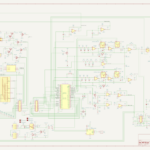

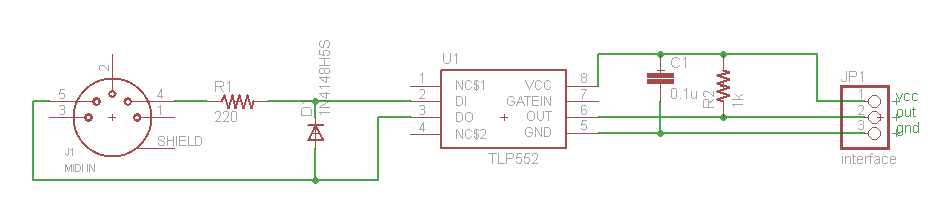

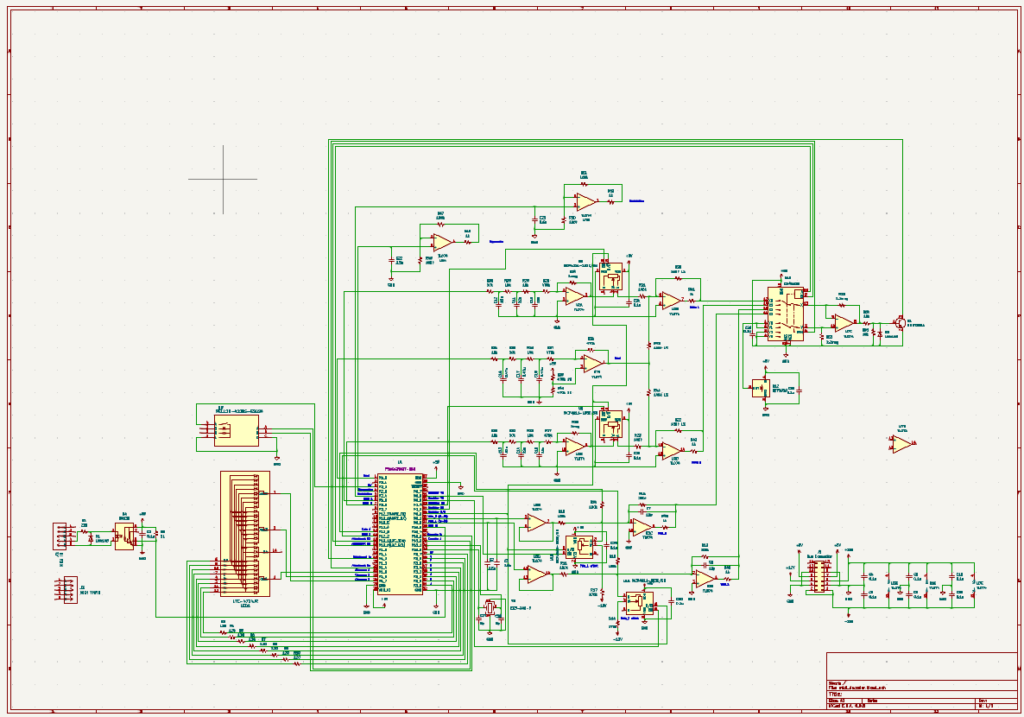

外付け部品が少なくて済むといってもやはりこれぐらいにはなってしまいました。しかしバラバラに思い浮かべていた妄想をこうやって一枚の回路図に落とし込んでいって、少しずつ全体の流れみたいなものが見えてくるのは楽しいです。

あと数日で回路図も固まりそうですが、これはまだ第0版、ゲートにベロシティー情報を載せる(アナログ的に)、自動のオフセット調整など、やったことのない試みが多いので心配なところは PoC (Proof of Concept) 実験をやる予定です。

その後は、実際に基板に載せるために回路図を機能基板部と制御基板部に分割する必要があります。その後基板レイアウトの設計。まーだまだ先は長いです。ちょっと気が遠くなるぐらいです。